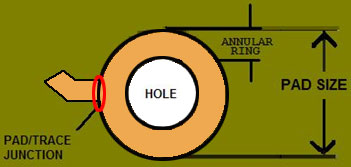

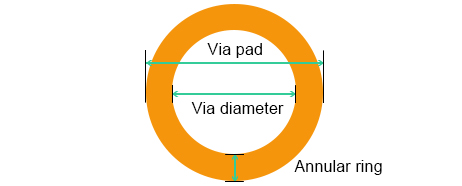

Ringringe

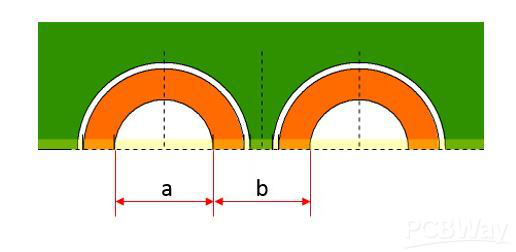

Der Kupferkissenbereich, der nach dem Bohren eines Lochs verbleibt, wird von

Lochkante zu Polsterkante gemessen.

Ihre inneren und äußeren Schichtpads sollten mindestens 0,018 "größer sein als

die Größe des Endlochs (0,010" für Durchkontaktierungen). Wenn Ihr Design ein

Pad zur Verfolgung der Mindestanforderungen für Verbindungsstellen enthält,

fügen Sie dieses zu den obigen Zahlen hinzu [0,018 "Pad + 0,002". Verbindung

sollte 0,020 "Pad haben]. Dies liefert einen 9-mil-Ring für Komponentenstifte

und einen 5-mil-Ring für Durchkontaktierungen.

Plattenmaterial

Eine Leiterplatte (PCB) unterstützt und verbindet elektronische Komponenten

mechanisch unter Verwendung von Leiterbahnen, Pads und anderen Merkmalen, die

aus Kupferblechen geätzt sind, die auf ein nichtleitendes Substrat laminiert

sind. Komponenten werden in der Regel auf die Platine gelötet.

1, Klassifizierung nach verstärkten Materialien (am häufigsten)

a. ein. Karton (FR-1, FR-2, FR-3)

b. Epoxidglasgewebe (FR-4, FR-5)

c. Verbundplatte (CEM-1, CEM-3)

d. HDI-Karte (RCC-Resin Coated Coppe)

e. Spezialplatte (Metallplatte, Keramikplatte usw.)

2, Klassifizierung nach den verschiedenen Harztypen

a. ein. Epoxidharz

b. Polyester Harz

c. PI-Harz (Polyimid)

3, Klassifizierung nach flammhemmenden Eigenschaften

a. ein. Flammschutzmittel (UL94-VO, UL94-V1)

b. Nicht flammhemmend (UL94-HB-Gehalt)

Brettdicke

Die langjährige Leiterplatten-Dicke nach Industriestandard beträgt 1/16 Zoll

(0,062 "). Zusätzlich zur Dicke von 0,062" sind die folgenden Dicken auch für

Limited Review-Produkte erhältlich: 0,031 ", 0,047", 0,093 "und 0,125". Die

Gesamtdickentoleranz liegt im Allgemeinen innerhalb von +/- 10% der angegebenen

Dicke (für 2- und 4-Schicht-Platten) und 14% für 6-Schicht-Platten.

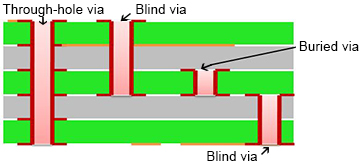

Blind Via und Buried Via

Was ist blind über und begraben über und was bedeuten sie für Ihr Projekt? Um

die Antwort zu verstehen, müssen wir zunächst wissen, welche

Durchkontaktierungen sich auf Leiterplatten beziehen.

Was ist eine Via?

Durchkontaktierungen sind die verkupferten Löcher in der Leiterplatte, durch

die die Schichten verbunden werden können. Die Standard-Durchkontaktierung wird

als Durchgangsloch-Durchkontaktierung bezeichnet. Die Verwendung von

Durchgangsloch-Durchkontaktierungen in der Surface Mount-Technologie (SMT)

bietet jedoch mehrere Nachteile. Aus diesem Grund verwenden wir stattdessen

häufig eine blinde Durchkontaktierung oder eine begrabene Durchkontaktierung.

Ein Blind oder vergrabenes Via kann in einer Vielzahl von verschiedenen

Maßnahmen verarbeitet werden, einschließlich einer verstopften Kupfermaske über,

einer verstopften Lötmaske über, einer plattierten über oder einer gestaffelten

über.

• Was ist eine Blind Via?

Bei einem Blind-Via verbindet das Via die äußere Schicht mit einer oder mehreren

inneren Schichten der Leiterplatte und ist für die Verbindung zwischen dieser

oberen Schicht und den inneren Schichten verantwortlich.

• Was ist eine begrabene Via?

In einer vergrabenen Durchkontaktierung sind nur die inneren Schichten der

Platine durch die Durchkontaktierung verbunden. Es ist im Inneren der Tafel

"vergraben" und von außen nicht sichtbar.

Blinde und vergrabene Durchkontaktierungen sind bei HDI-Leiterplatten besonders

vorteilhaft, da sie die Dichte der Leiterplatten optimieren, ohne die

Leiterplattengröße oder die Anzahl der benötigten Leiterplattenschichten zu

erhöhen.

• Was ist eine gestapelte Via und Microvia?

Ein gestapeltes Via ist eine Möglichkeit, die Überlegungen zu Größe und Dichte

bei der Herstellung von Leiterplatten weiter zu verbessern - Faktoren, die bei

der heutigen Miniaturisierung und den Anforderungen an die

Übertragungsgeschwindigkeit bei hohen Signalen in vielen Anwendungen äußerst

wichtig sind.

Wenn Sie blinde Durchkontaktierungen mit einem Seitenverhältnis von mehr als 1:

1 haben oder Ihre Bohranforderungen mehrere Schichten abdecken, kann eine

gestapelte Durchkontaktierung der beste Weg sein, um eine zuverlässige interne

Verbindung herzustellen.

Gestapelte Durchkontaktierungen sind laminierte blinde oder vergrabene

Durchkontaktierungen, mehrere Durchkontaktierungen innerhalb einer Leiterplatte,

die um dasselbe Zentrum herum zusammengesetzt sind. Versetzte

Durchkontaktierungen sind laminierte Durchkontaktierungen, die sich nicht in der

Mitte befinden. Zu den Vorteilen gestapelter Durchkontaktierungen gehören nicht

nur Platzersparnis und zunehmende Dichte, sondern auch eine größere Flexibilität

hinsichtlich der inneren Verbindungen, eine bessere Routing-Kapazität und eine

geringere parasitäre Kapazität. Der Nachteil von gestapelten

Durchkontaktierungen besteht darin, dass sie mit höheren Kosten verbunden sind

als Standard-Durchkontaktierungsdurchkontaktierungen oder blinde / vergrabene

Durchkontaktierungen.

Eine Mikrovia ist nur eine sehr kleine Durchkontaktierung. Wie Sie sich

vorstellen können, sind Mikrovias für Leiterplattenentwickler sehr wünschenswert

- je kleiner der Durchmesser, desto mehr Routing-Platz auf der Platine und desto

geringer die parasitäre Kapazität, die für Hochgeschwindigkeitsschaltungen

unerlässlich ist. Sehr kleine Durchkontaktierungen erfordern jedoch auch mehr

Bohrzeit und mehr außermittige Bewegungen. Mikrovias als Vias mit Durchmessern

von weniger als oder gleich 0,1 mm.

• Via Typ Via Durchmesser

|

Über Typ

|

Über Durchmesser

(max.)

|

Über Durchmesser

(Mindest.)

|

Über Pad

|

Ring

|

Seitenverhältnis

|

|

Blind via (mechanisch)

|

0.4mm

|

150μm

|

450μm

|

127μm

|

1:1

|

|

Blind via (Laser)

|

0.1mm

|

100μm

|

254μm

|

150μm

|

1:1

|

|

Begraben über (mechanisch)

|

0.4mm

|

100μm

|

300μm

|

150μm

|

1:10

|

|

Begraben über (Laser)

|

0.4mm

|

100μm

|

225μm

|

150μm

|

1:12

|

Komponentenseite

Um Ihre Leiterplatte korrekt zu bauen, müssen wir in der Lage sein, die richtige

Ausrichtung Ihres Designs zu ermitteln. Komponente, Ebene 1 oder oberste Ebene

sollten nach oben eingelesen sein. Alle anderen Ebenen sollten so ausgerichtet

sein, als würden sie durch das Brett schauen. Bitte verwenden Sie

Ebenenbezeichner, gehen Sie durch Markierungen oder korrigieren Sie den Text der

Leseebene.

Kontrollierte Impedanz

Das elektrische Ergebnis der Herstellung einer Leiterplatte zur Erfüllung der

charakteristischen Impedanzspezifikationen. Die Kombination von Kupferdicke und

Linienbreite sowie die dielektrische Dicke und die Eigenschaften des

Grundmaterials tragen alle zum Impedanzwert bei.

Die charakteristische Impedanz erweitert das Konzept des Widerstands gegen

Wechselstromkreise und beschreibt nicht nur die relativen Amplituden von

Spannung und Strom, sondern auch die relativen Phasen. Wenn die Schaltung mit

Gleichstrom (DC) betrieben wird, gibt es keinen Unterschied zwischen Impedanz

und Widerstand. Letzteres kann als Impedanz mit einem Phasenwinkel von Null

betrachtet werden.

Kupfer (fertiges Kupfer) Gewicht

Dies ist die Gesamtdicke von Kupfer auf der Plattenoberfläche. Der Wert wird aus

der Kupferfoliendicke plus plattiertem Kupfer minus Kupfer bestimmt, das während

der Oberflächenvorbereitung entfernt wurde. Das Kupfergewicht wird in Unzen /

Quadratfuß gemessen. 1 Unze / Quadratfuß = 0,0012 Zoll Mindestdicke (Höhe). Wir

bieten fertiges Kupfergewicht von 1 Unze, 2 Unzen und 3 Unzen. Für

mehrschichtige Leiterplatten bieten wir an (1 Unze und 2 Unze Kupferschichten).

Bohrdatei (auch bekannt als Excellon-Bohrdatei)

Dies ist ein Beispiel für ein Excellon-Drill-Dateiformat. Es hat sowohl X- als

auch Y-Koordinaten sowie Werkzeuggrößen. Dies kann in jedem Texteditor

(Notizblock) angezeigt werden. Dies ist die Datei, die Ihre fertigen Lochgrößen

und -positionen regelt.

Beispiel für ein Excellon-Dateiformat:

M48 INCH

LZ T01C0.015

T02C0.031

T03C0.034

T04C0.037

T05C0.052

T06C0.058

%

T01

X00165Y-03805

X0018Y-03235

X00265Y-00704

X00281Y-01349

X00302Y-03816

![]() Elektrischer test

Elektrischer test

Prüfung des elektrischen Durchgangs (offen) und der Isolation (kurzgeschlossen)

von Leiterplatten. Aus den vom Kunden bereitgestellten Gerber-Dateien wird eine

Netzliste erstellt und dann elektrisch mit der fertigen Platine verglichen. Die

Lötmaskenschicht dient als Maske, um zu bestimmen, welche Punkte getestet werden

können. Im Allgemeinen werden Endpunkte aller Netze zum Testen programmiert, es

sei denn, sie sind mit einer Lötmaske abgedeckt. In diesem Fall wird der dem

Endpunkt am nächsten liegende Testpunkt getestet. Die verwendeten

Standardtestparameter sind 100 Volt, Isolationswiderstand von 10 M Ohm,

Isolationsabstand 0,050 Zoll und Durchgangswiderstand von 50 Ohm.

Sunstone Circuits verwendet die Flying Probe (Fixtureless) -Technologie, um

unsere elektrischen Tests durchzuführen. Wir empfehlen, alle

oberflächenmontierten Platinen und mehrschichtigen Bestellungen zu testen.

Es ist nicht möglich, Boards mit Siebdruck auf Pads genau zu testen. Es wird

dringend empfohlen, die Option für Siebdruckclips bei elektrisch getesteten

Bestellungen auszuwählen.

ENIG (Chemisches Nickel-Immersionsgold)

RoHS-konforme Oberflächenbeschaffenheit, die auch sehr eben (flach) und

langlebig ist. ENIG wird für Tight Pitch-, IC- und BGA-Technologie empfohlen. Es

bietet eine gute Lötstelle, lässt Teile sehr flach sitzen, hält mehreren

Reflow-Zyklen sowie der Lagerung von Leiterplatten stand.

Chemische Abscheidung - Die Abscheidung von leitendem Material aus einer

autokatalytischen Beschichtungslösung ohne Anlegen von elektrischem Strom.

Tauchbeschichtung - Die chemische Abscheidung einer dünnen Metallbeschichtung

auf bestimmten Basismetallen, die durch eine teilweise Verschiebung des

Basismetalls erreicht wird.

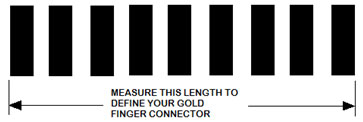

Goldfinger (lineare Zoll)

Mit Nickel (Ni) und Hartgold (Au) galvanisierte Kantenverbinder, gut geeignet

für Verschleißanwendungen, die für PCBpro- und Custom-Produkte erhältlich sind.

(Ca. 200 u ”Ni / Min. 30 u” Au). Verwendung des branchenüblichen

Verbindungsstab-Beschichtungsprotokolls, um das Galvanisieren von Ni und Au nach

dem Ätzen und dem Aufbringen der Lötmaske zu ermöglichen. Der Preis wird anhand

des Abstands (lineare Zoll) zwischen den Außenkanten der äußersten

Steckerkontakte berechnet.

Designer-Tipp: Möglicherweise nicht für Anwendungen geeignet, bei denen mehrere

Fingerlängen erforderlich sind.

Mit Ihrer Au-Auswahl wird Ihrem Randverbinder eine

Standard-30-Grad-Abschrägung hinzugefügt. Auf Anfrage können wir auch bei 15

oder 45 Grad abschrägen. Bei mehrschichtigen Platten stellen Sie bitte sicher,

dass die Innenschicht ausreichend zurückgesetzt ist, um die gewünschte

Abschrägung zu ermöglichen.

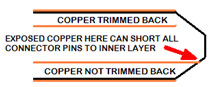

Bei Goldfinger-Steckverbindern ist die Vorderkante normalerweise abgeschrägt, um

das Einsetzen in den Gegenstecker zu erleichtern. In diesem Fall können innere

Ebenen Kupfer freiliegen, wenn sie nicht ausreichend von der Kante zurückgezogen

werden. Wir ziehen Ihre innere Kupferschicht wie oben rechts gezeigt zurück, um

zu vermeiden, dass Kupfer an dieser Stelle freigelegt wird. Freiliegendes Kupfer

kann beim Einstecken einen direkten Kurzschluss an allen Anschlüssen Ihres

Steckers verursachen

HASL (Heißluftlötstufe)

Der Prozess des Hinzufügens von Lot zu den freiliegenden Kupfermerkmalen der

Leiterplatte. Das Verhältnis von Zinn zu Blei in der Lagerstätte beträgt

ungefähr 60% / 40%. Fertige Platten werden in ein geschmolzenes Lötbad getaucht

und durch einen Hochdruckstrom heißer Luft geleitet, um überschüssiges Lot zu

entfernen, was dazu führt, dass eine gleichmäßige Lötschicht auf alle

freiliegenden Kupferoberflächen aufgebracht wird. HASL ist keine ideale Wahl für

die Oberflächenbeschaffenheit bei engen Abständen oder für ICs und BGAs. Die

Löthöhe wird von Pad zu Pad variieren, und die Planarität ist keine Stärke von

HASL. Bitte wählen Sie für diese Designs Immersionssilber oder ENIG. Kein

RoHS-konformes Finish.

Halblöcher (Castellated Holes)

Überzogene halbe Löcher (Kastelllöcher) sind Löcher, die vom Rand der mit

plattierten Brettern abgesetzt sind

Kupfer nach einem speziellen Verfahren. Es wird hauptsächlich für

Board-on-Board-Verbindungen verwendet, meistens dort, wo zwei Leiterplatten mit

unterschiedlichen Technologien kombiniert werden.

Durch die direkte Verbindung der Leiterplatten ist das gesamte System erheblich

dünner als eine vergleichbare Verbindung mit mehrpoligen Steckverbindern. Die

plattierten Kanten sind auch bei der Herstellung von Mini-Leiterplattenmodulen

nützlich.

Beschichtete halbe Löcher sind sowohl in Standardplatinen als auch in

fortgeschrittenen Platinen erhältlich. Für den Standard-PCB-Service beträgt der

Mindestdurchmesser der Kastelllöcher 0,6 mm. Wenn Sie kleinere Kastelllöcher

benötigen, bitten Sie unseren Verkauf, einen erweiterten PCB-Service anzubieten.

Der Mindestabstand zwischen zwei plattierten Halblöchern beträgt 0,55 mm.

Wie werden die plattierten halben Löcher hergestellt? Die Beschichtung wird

durch Zurücksetzen der Kupferschale vor mechanischer Beschädigung geschützt.

Daher können die plattierten Halblöcher präzise gefräst werden und die

Prozesssicherheit stark verbessern

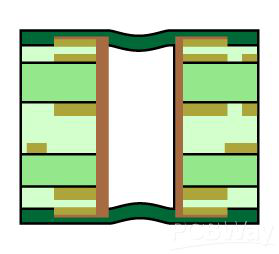

Ebenenfolge

Sie müssen die Layer aus Ihren Dateien während des Bestellvorgangs nicht

zuordnen, um Zeit zu sparen. Um sicherzustellen, dass wir die Ebenen in der

richtigen Reihenfolge erstellen, geben Sie eine Readme-Datei mit der

Ebenenreihenfolge an oder benennen Sie die Dateien auf logische Weise. Zum

Beispiel:

copper_top.grb

inner1.grb

inner2.grb

copper_bot.grb

silk_top.grb

silk_bot.grb

smask_top.grb

smask_bot.grb

paste_top.grb

paste_bot.grb

ncdrill.txt

drill_dwg.grb

fab_dwg.grb

Schichtaufbau

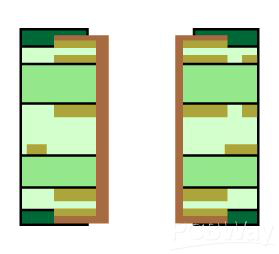

Stapelbildung bezieht sich auf die Anordnung von Kupferschichten und

Isolierschichten, aus denen eine Leiterplatte vor dem Entwurf des

Leiterplattenlayouts besteht. Während ein Schichtstapel es Ihnen ermöglicht,

mehr Schaltkreise auf einer einzelnen Platine durch die verschiedenen

Leiterplattenschichten zu erhalten, bietet die Struktur des PCB-Stapelaufbaus

viele andere Vorteile:

. Ein PCB-Layer-Stack kann Ihnen dabei helfen, die Anfälligkeit Ihrer Schaltung

für externes Rauschen zu minimieren, die Strahlung zu minimieren und Impedanz-

und Übersprechprobleme bei Hochgeschwindigkeits-PCB-Layouts zu reduzieren.

. Ein guter Schicht-PCB-Stapel kann Ihnen auch dabei helfen, Ihren Bedarf an

kostengünstigen, effizienten Fertigungsmethoden mit Bedenken hinsichtlich

Signalintegritätsproblemen in Einklang zu bringen

. Der richtige PCB-Schichtstapel kann auch die elektromagnetische Verträglichkeit

Ihres Designs verbessern.

Warum muss gestapelt werden?

Vor dem Entwurf einer mehrschichtigen Leiterplatte müssen Entwickler zunächst

die Leiterplattenstruktur basierend auf der Größe der Schaltung, der Größe der

Leiterplatte und den EMV-Anforderungen bestimmen. Das heißt, entscheiden Sie, ob

Sie 4 Schichten oder 6 Schichten verwenden möchten. Weitere

Leiterplattenschichten. Nachdem die Anzahl der Schichten bestimmt wurde, werden

die Platzierung der inneren Schicht und die Verteilung verschiedener Signale auf

diesen Schichten bestimmt.

Die Planung der mehrschichtigen PCB-Stapelkonfiguration ist einer der

wichtigsten Aspekte, um die bestmögliche Leistung eines Produkts zu erzielen.

Ein schlecht gestaltetes Substrat mit ungeeignet ausgewählten Materialien kann

die elektrische Leistung der Signalübertragung beeinträchtigen und die

Emissionen und das Übersprechen erhöhen. Außerdem kann das Produkt anfälliger

für externe Störungen werden. Diese Probleme können aufgrund von Zeitstörungen

und Interferenzen zu einem intermittierenden Betrieb führen, wodurch die

Leistung des Produkts und die langfristige Zuverlässigkeit erheblich

beeinträchtigt werden. Im Gegensatz dazu kann ein ordnungsgemäß aufgebautes

PCB-Substrat elektromagnetische Emissionen und Übersprechen wirksam reduzieren

und die Signalintegrität verbessern, wodurch ein Stromverteilungsnetz mit

niedriger Induktivität bereitgestellt wird. Und aus Sicht der Herstellung kann

auch die Herstellbarkeit des Produkts verbessert werden.

Minimale Spuren und Abstände

Die Trace-Breite und der Abstand zwischen den Traces werden verwendet, um die

Komplexität Ihres Designs zu definieren. Wir verwenden diese Informationen für

die Preisgestaltung und um Ihre Bestellung in unseren Herstellungsprodukten

richtig auszurichten. Je kleiner oder dichter die Eigenschaften Ihres Boards

sind, desto schwieriger wird die Herstellung. Bei der Bestellung Ihrer Platinen

müssen Sie die minimale Spurgröße sowie den minimalen Kupfer-Kupfer-Abstand

kennen, der in Ihrem Design vorhanden ist.

Nicht plattierte Löcher (NPTH)

Ein Loch in einer Leiterplatte, das keine Beschichtung oder andere Art von

leitfähiger Verstärkung enthält. Wird im Allgemeinen zur Montage von Komponenten

auf einer Leiterplatte oder einer Leiterplatte an einem größeren Teil eines

Projekts verwendet.

Wir empfehlen, dass Sie eine Bohrzeichnung beifügen, um die nicht plattierten

Löcher in Ihrem Entwurf zu identifizieren.

Nicht plattierte Löcher sollten einen Mindestabstand von 0,010 Zoll zu leitenden

Oberflächen einhalten.

Durchlöcher plattiert (PTH)

Ein Loch mit einer Beschichtung an den Wänden, das eine elektrische Verbindung

zwischen leitenden Mustern auf inneren Schichten, äußeren Schichten oder beiden

einer Leiterplatte herstellt.

Alle Bohrergrößen werden als PTH behandelt, es sei denn, NPTH ist in der

Textdatei Zeichnung, Druck, Bohrdatei, Beschreibung des Bohrwerkzeugs angegeben

oder mit einem speziellen Hinweis gekennzeichnet, z. B. „0,125 nicht zu

plattierende Löcher“. Außerdem werden landlose Löcher identifiziert In den

Gerber-Dateien werden sie als nicht plattiert behandelt: Löcher ohne Pads,

Löcher mit einem Fadenkreuz oder Löcher mit einem deutlich kleineren Pad (dh

0,125 "Löcher mit 0,050" nicht unterstützten Pads).

Alle Löcher in der Bohrdatei, unabhängig von der Definition, werden als

plattierte Löcher behandelt. Dies bedeutet, dass die Lochgröße erhöht wird, um

die Beschichtung aufzunehmen, am Primärbohrer gebohrt wird und möglicherweise

plattiert wird oder nicht (abhängig vom Vorhandensein von Pads, der Nähe zu

Kupfermerkmalen oder der Größe des Bohrlochs).

Wenn sich die Zeichnung oder Werkzeugbeschreibung von der in der Bohrdatei

angegebenen Größe unterscheidet, verwenden wir die Bohrdatei, um die Größe des

fertigen Lochs zu bestimmen (für „Full Review“ (NRE) werden diese Fehler zur

Klärung durch den Kunden gemeldet, bevor mit der Herstellung begonnen werden

kann).

Alle Bestellungen, die als „1 Schicht“ aufgegeben werden, werden einseitig

behandelt und die Lochfässer werden nicht plattiert.

Oberflächenfinish

Es gibt viele Arten von Oberflächenbehandlungen, die hauptsächlich mit 5 Typen

gezeigt werden: HASL, OSP, ENIG, Immersionszinn und Immersionssilber.

HASL oder HASL LF:

HASL sollte die am weitesten verbreitete Oberflächenbehandlungstechnologie sein.

Wenn die heiße Luft eingeebnet wird, bilden das Lot und das Kupfer an der

Verbindungsstelle eine Kupfer-Zinn-Metallverbindung, und ihre Dicke beträgt

ungefähr 1 bis 2 mil. HASL bietet eine sehr zuverlässige Lötverbindung und

Haltbarkeit. HASL macht das Löten von Bauteilen sehr effektiv, aber aufgrund der

Dicke der HASL-Beschichtung kann die Ebenheit der Oberfläche für Bauteile mit

feiner Teilung ungeeignet sein. Die HASL-Ablagerung besteht aus einer

eutektischen Mischung aus Zinn und Blei.

ENIG (Immersionsgold):

ENIG ist nur ein Prozess, der eine dicke Schicht einer Nickel-Gold-Legierung mit

guten elektrischen Eigenschaften über Kupfer bedeckt und einen Langzeitschutz

für Leiterplatten verarbeitet, um hervorragende mechanische Eigenschaften zu

erreichen. Darüber hinaus hält die ENIG-Oberfläche die besondere Toleranz

gegenüber der Umgebung, die andere Oberflächen nicht erfüllen. Seine Fähigkeit,

die Auflösung des Kupfers zu verhindern, bringt auch eine gute Leistung beim

bleifreien Löten.

OSP: Die OSP-Oberfläche (Organic Solder Capability Conservative) ist ein

Verfahren zur chemischen Erzeugung einer Schicht aus organischem Film über

klarem blankem Kupfer. Diese Schicht aus organischem Film ist beständig gegen

Oxidation, Wärmeschock und Benetzung, wodurch die Kupferoberfläche unter

normalen Bedingungen vor Rost geschützt wird. In der Zwischenzeit konnte es auch

beim anschließenden Hochtemperaturschweißen zum besseren Löten leicht entfernt

werden. Sein einfacher Prozess und seine geringen Kosten bringen seine breite

Verwendung in der Leiterplattenproduktion mit sich.

Immersionssilber: Der Immersionssilberprozess ist relativ einfach und schnell.

Es ist nicht erforderlich, eine dicke Panzerungsschicht auf die Leiterplatte

aufzubringen, sondern bietet auch eine gute elektrische und Lötfähigkeit für die

Leiterplatte in einer heißen, nassen und verschmutzten Umgebung. Der Nachteil

ist, dass es seinen Glanz verliert. Und es hat auch gute Lagereigenschaften.

Immersionszinn: Die Immersionszinnoberfläche wird aufgrund ihrer guten Ebenheit

und bleifreien Natur verwendet. Dabei entstehen jedoch leicht intermetallische

Cu / Sn-Verbindungen mit schlechter Lötfähigkeit. Die größte Schwäche der

Immersionszinnoberfläche ist ihre kurze Lebensdauer, insbesondere wenn sie in

Umgebungen mit hohen Temperaturen und hoher Luftfeuchtigkeit gelagert wird. Die

intermetallischen Cu / Sn-Verbindungen nehmen bis zum Verlust der Lötfähigkeit

zu.

· Vergleich von Kosten und Lötbarkeit

Kosten: Galvanisieren von Nickelgold> ENIG> Immersionssilber>

Immersionszinn> HASL> OSP.

Tatsächliche Lötbarkeit: Galvanisieren von Nickelgold> HASL> OSP>

ENIG> Immersionssilber> Immersionszinn

Die Oberflächenbeschaffenheit der Leiterplatte ist eine Beschichtung zwischen

einer Komponente und einer Leiterplatte mit blanken Leiterplatten. Es wird aus

zwei grundlegenden Gründen angewendet: um die Lötbarkeit sicherzustellen und um

freiliegende Kupferschaltungen zu schützen. Da es viele Arten von Oberflächen

gibt, ist die Auswahl der richtigen keine leichte Aufgabe, zumal

Oberflächenhalterungen komplexer geworden sind und Vorschriften wie RoHS und

WEEE die Industriestandards geändert haben.

HASL (Hot Air Solder Leveling) / bleifreies HASL

HASL ist die in der Industrie vorherrschende Oberflächenbeschaffenheit. Der

Prozess besteht darin, Leiterplatten in einen geschmolzenen Topf aus einer Zinn

/ Blei-Legierung einzutauchen und dann das überschüssige Lot mit Luftmessern zu

entfernen, die heiße Luft über die Oberfläche der Leiterplatte blasen.

Vorteile: Kostengünstig, verfügbar, reparierbar

Nachteile: Unebene Oberflächen, Nicht gut für Komponenten mit feiner Teilung,

Thermoschock, Nicht gut für plattierte Durchgangslöcher (PTH), Schlechte

Benetzung

OSP (Organic Solderability Preservative)

OSP ist eine organische Oberfläche auf Wasserbasis, die typischerweise für

Kupferpads verwendet wird. Es verbindet sich selektiv mit Kupfer und schützt das

Kupferkissen vor dem Löten. OSP ist umweltfreundlich, bietet eine koplanare

Oberfläche, ist bleifrei und erfordert nur geringe Wartung der Geräte. Es ist

jedoch nicht so robust wie HASL und kann bei der Handhabung empfindlich sein.

Vorteile: bleifrei, flache Oberfläche, einfacher Vorgang, reparierbar

Nachteile: Nicht gut für PTH, empfindlich, kurze Haltbarkeit

ENIG (Chemisches Nickel-Immersionsgold)

ENIG wird schnell zum beliebtesten Oberflächenfinish der Branche. Es handelt

sich um eine zweischichtige Metallbeschichtung, bei der Nickel sowohl als

Barriere für das Kupfer als auch als Oberfläche dient, auf die Komponenten

gelötet werden. Eine Goldschicht schützt das Nickel während der Lagerung. ENIG

ist eine Antwort auf wichtige Branchentrends wie bleifreie Anforderungen und das

Aufkommen komplexer Oberflächenkomponenten (insbesondere BGAs und Flip-Chips),

die flache Oberflächen erfordern. ENIG kann jedoch teuer sein und manchmal zu

einem sogenannten „Black-Pad-Syndrom“ führen, einem Phosphoraufbau zwischen den

Gold- und Nickelschichten, der zu Bruchflächen und fehlerhaften Verbindungen

führen kann.

Vorteile: Flache Oberflächen, stark, bleifrei, gut für PTH

Nachteile: Black-Pad-Syndrom, teuer, nicht gut für Nacharbeiten

Schablone

Der einzige Zweck einer Schablone besteht darin, Lötpaste auf eine blanke

Leiterplatte zu übertragen. Eine rostfreie Folie wird lasergeschnitten, wodurch

eine Öffnung für jedes oberflächenmontierte Gerät auf der Platine entsteht.

Sobald die Schablone richtig auf der Platte ausgerichtet ist, wird Lötpaste über

die Öffnungen aufgetragen (ein einziger Durchgang mit einer Metallrakelklinge).

Wenn die Folie von der Platte getrennt wird, verbleiben Lötpastensteine, die zum

Platzieren des SMD bereit sind. Dieser Prozess sorgt im Gegensatz zu

Handlötverfahren für Konsistenz und spart Zeit.

Foliendicke und Öffnungsgröße der Öffnung steuern das Volumen der auf der Platte

abgelagerten Paste. Zu viel Lötpaste führt zu Lötballenbildung, Überbrückung und

Grabsteinbildung. Ein Mangel an Lötpaste führt zu unzureichenden Lötstellen. All

dies beeinträchtigt die elektrische Funktionalität der Platine.

Die richtige Foliendicke wird basierend auf den Gerätetypen ausgewählt, die

auf die Platine geladen werden. Komponentenpakete wie 0603-Kondensatoren oder

SOICs mit 0,020-Zoll-Teilung erfordern eine dünnere Schablone als größere

Gehäuse wie 1206-Kondensatoren oder SOICs mit 0,050-Zoll-Teilung. Die

Schablonendicke reicht von 0,001 "bis 0,030". Die typische Foliendicke, die bei

den meisten Platten verwendet wird, liegt zwischen 0,004 und 0,007 Zoll.

Über Abdeckung

Durchkontaktierungen nicht abgedeckt

Dies bedeutet, dass die Durchkontaktierungen freigelegt sind und die

Oberflächenbeschaffenheit über einen Lauf aufgetragen wird.

Die Lötpaste kann in die Durchkontaktierungen gelangen und schlechte oder

nicht vorhandene Lötstellen verursachen.

Zeltvias

Dies bedeutet, dass die Durchkontaktierungen einfach mit Lötmasken-Tinte

abgedeckt werden. Während der Herstellung sind keine zusätzlichen

Prozessschritte erforderlich.

Abdecken des Ringes und der Durchkontaktierungen mit Lötmasken-Tinte, um eine

Exposition gegenüber den Elementen zu vermeiden und einen versehentlichen

Kurzschluss oder Kontakt mit dem Stromkreis zu verringern.

Verstopfte Durchkontaktierungen mit nicht leitenden Medien (z. B. Epoxid / Harz,

Lötmasken-Tinte)

Die leitenden Durchkontaktierungen in BGA erfordern angeschlossene

Durchkontaktierungen. Da Lötpaste vom vorgesehenen Pad wegsaugen und in die

Durchkontaktierung fließen kann, entstehen beim Zusammenbau schlechte oder nicht

vorhandene Lötstellen.

Der Durchmesser der verstopften Durchkontaktierungen muss kleiner als 0,5 mm

sein.